The Challenge

BetaThe Signaloid C0-microSD is a tiny programmable FPGA System-on-Module (SoM) that makes it possible to extend your existing industrial automation, manufacturing, and robotics systems with an FPGA-based hardware accelerator. It comes in a microSD form factor, fits in any unused SD or microSD slot, and can be interfaced with as a standard SD block device. This makes it possible, for the first time, to implement hardware acceleration for many data-processing tasks at the edge, even if your system lacks traditional expansion options such as a PCIe M.2 slot!

This FPGA platform has two main use cases: (1) use it as a hot-pluggable FPGA module, or (2) use it as a hot-pluggable Signaloid C0 RISC-V co-processor module. When plugged into a host computer, it appears as an empty and unformatted SD storage device. Developers can easily load custom FPGA bitstreams and applications for the built-in Signaloid SoC via the SD interface.

A Hot-Pluggable FPGA ModuleWhen using the Signaloid C0-microSD as a hot-pluggable FPGA SoM, developer can plug it into their computer, flash new FPGA bitstreams, and then either plug it into a breadboard using a microSD breakout board or integrate it into a legacy (or custom) PCB that has an unused microSD slot. Once powered on, the built-in bootloader will check if the device has been connected to an SD host, and if not, will load the latest custom user bitstream. In this configuration, the C0-microSD offers six configurable I/O pins by repurposing the microSD pads, and five additional I/O pins in the form of test pads.

A Hot-Pluggable Co-Processor ModuleIf developer don’t wish to load a custom FPGA design, the Signaloid C0-microSD comes preloaded with a version of Signaloid’s C0 RISC-V processor SoC, which one can use to run their own applications. In this mode, host computers can use the SD protocol to exchange data with applications running on the Signaloid C0-microSD.

Signaloid C0-microSD can be integrated into existing embedded systems that feature slots for microSD cards. These range from low-power development boards, to handheld gadgets, to Programmable Logic Controllers (PLCs) for industrial automation.

Applications running on the Signaloid C0-microSD’s C0 processor SoC can take advantage of a subset of Signaloid's uncertainty-tracking technology to quantify how uncertainties in data affect their outputs.

Hardware Spec:Lattice ICE40UP5K FPGA

- 5280 logic cells

- 120 Kbit dual-port block RAM

- 1 Mbit (128 KB) single-port RAM

Renesas AT25QL128A SPI Flash

- 128 Mbit (16 MiB) non-volatile memory

Programmable I/O pins:

- Two on-board LEDs (one red and one green) for status indication.

- Six programmable I/O pins (from the microSD interface)

- Five additional programmable pins on test pads

Built-in Signaloid C0 RISC-V processor SoC

Built-in bootloader, allowing you to load new FPGA bitstreams or RISC-V applications via the SD interface

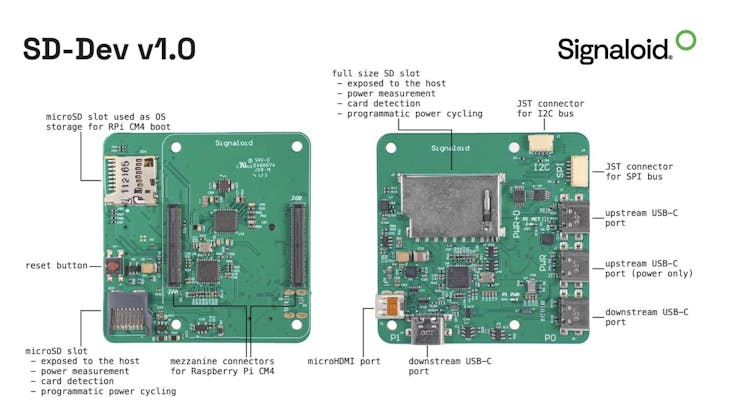

The SD-Dev carrier boardSignaloid SD-Dev is an optional compact carrier board and development system for testing and characterizing the Signaloid C0-microSD.

When you connect the Signaloid SD-Dev to a host computer via USB, it acts as a generic USB-to-SD adapter, exposing one microSD and one full-size SD slot to the host (peripheral mode). Alternatively, you can attach a Raspberry Pi CM4 to the carrier board, producing a compact SBC with hot-swappable FPGA modules in a standalone configuration. In this mode, the carrier board provides power-measurement capabilities for the on-board FPGA modules and allows you to power cycle them programmatically.

The carrier board features:

- 2 USB Type-C downstream ports

- 1 USB Type-C upstream port

- 1 USB Type-C upstream power-only port

- 1 Micro HDMI port

- JST connectors for SPI and I²C peripherals

- One full-size SD slot and one microSD slot for Signaloid C0-microSD boards or regular storage cards

- SD card detection

- Programmable power cycling

- Power measurement

- Open-top microSD socket allows you to probe the Signaloid C0-microSD debug pads

- Dual function (peripheral and standalone modes)

- Board outline of 57 x 57 mm

Prizes

Selected PRO members will receive cash payout upon project delivery.

Gig Payout

Contest Status

Learn more about PROTimeline

Challenge begins

March 5, 2025 at 12:00 PM PST

Proposal submissions close

August 5, 2025 at 12:00 PM PDT

Contenders announced

August 5, 2025 at 8:00 PM PDT

Solutions due

August 15, 2025 at 12:00 PM PDT

Solutions revealed

Aug 15, 2025